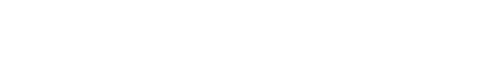

当前,无线通信、汽车电子、医疗影像等领域快速发展,持续推动新一代ADC和DAC向更高分辨率与更高采样率不断突破。作为模块间数据交互的核心支撑,高速接口技术同步迎来迭代升级。JESD204接口标准应运而生,通过高速串行链路实现转换器与FPGA、ASIC之间高效稳定的数据传输,有效优化并行接口在引脚数量、时序对齐等方面的设计复杂度,成为高速数据转换领域的主流技术方向。

图1:JESD204接口链路示意图

高端数据转换器芯片的研发与落地,不仅依赖转换器本身的模拟设计能力,同样离不开配套高速接口 IP 的稳定支撑。

JESD204作为当今高速模数转换接口的事实标准,市场应用成熟度高,相关方案选择丰富。面向多样化的市场需求与应用场景,具备本地化研发与服务优势的解决方案,能够为行业带来更灵活、更贴合实际场景的技术选择,助力产业链高效协同与持续创新。

JESD204B/C:以速率与可靠性支撑高速传输需求

JESD204B与JESD204C是目前应用最广泛的两个版本标准,它们在传输效率、同步机制与链路稳健性等方面持续优化,适配不同层级的高速传输场景,在多个维度展现出了独特优势。

传输速率与编码效率方面,JESD204B将最大通道速率从3.125Gbps提升至12.5Gbps,采用8b/10b编码;而JESD204C进一步将最大通道速率提升至32Gbps,引入64b/66b编码,使编码开销有效降低至3%,显著提升数据吞吐能力。

同步机制上,JESD204B引入确定性延迟机制,并通过补充子类(Subclass)概念,使设计兼容不同的同步场景和速率要求,其中子类1/2确保数据从输入至输出的延迟在上电周期和链路复位后重复可控。JESD204C在64b/66b编码模式下通过应用层软件处理优化同步初始化流程,同时SYSREF以新引入的本地扩展多块时钟(LEMC)替代传统的LMFC方式,为确定性延迟提供了更灵活的实现路径。

链路稳健性同样有所增强。面对更高传输速率下的信号完整性要求,JESD204C引入可选的前向纠错(FEC)功能,基于法尔码实现单突发错误校正。此外,新标准将物理层划分为B类和C类,其中C类进一步细分为C-S、C-M、C-R三个子类,以适配不同的功耗和均衡需求。

牛芯JESD204 IP方案:兼顾灵活适配与稳定可靠

牛芯长期专注于JESD204收发解决方案的研发,提供JESD204B/C TX/RX “PHY+Controller”完整集成IP方案,兼顾信号完整性、协议兼容性与落地便利性。

在自适应均衡与时钟架构上,204 PHY TX使用3 Tap FFE提升信号完整性,并使用片内端接阻抗校准,除去片外电阻和额外芯片引脚,简化PCB设计;204 PHY RX采用自适应CTLE以及5 Tap DFE协同工作,适配不同长度的PCB走线或线缆。在时钟方案上,204 Controller 采用分离的clk_serdes、clk_character、clk_sample多时钟域设计,支持灵活的系统时钟架构,并可自动或手动配置Sample时钟与Character时钟比率,覆盖不同应用场景。

在协议支持方面,该方案完全兼容JESD204C(2017年12月版)和JESD204B.01标准,支持8b/10b(JESD204B)+64b/66b、64b/80b(JESD204C)编码,全面覆盖子类0/1/2。在64b/66b模式下,可选配前向纠错(FEC)功能,可纠正长达9比特的突发错误,从而有效提升链路鲁棒性。

在通道配置与集成便利性上,该方案支持通道数灵活定制,用户可根据系统总带宽需求调整。RX支持物理通道到逻辑通道的Crossbar映射,每个逻辑通道均可通过MUX选择任意物理通道源。集成方案方面,方案支持180度镜像翻转和相邻多PHY直接拼接,便于通道扩展。

良好的可替代性也是方案的一大亮点。牛芯实现的204 PHY在PAD/Bump布局上对标前沿产品,既能保证pin-to-pin兼容,也支持自定义,实现良好的原位替换,可广泛适用于激光雷达、医学成像、卫星通信等多个领域。

依托稳定的设计与完善的验证体系,牛芯半导体JESD204 IP方案已助力多家行业厂商完成ADC芯片的研发与量产,产品具备多速率覆盖,多通道灵活配置、多封装与多工艺节点适配能力。其中,TX端产品矩阵可覆盖6.4Gbps至25Gbps的通道最高速率,支持X4/X8/X16通道个数灵活配置,适配1.8-2.5V IO电压、0.9-1.0V core电压、Wirebond/Flip-Chip封装和22nm至180nm的工艺节点;RX端产品则实现了12.5Gbps至16Gbps速率覆盖,X4/X8通道可配,支持28nm工艺节点和Flip-Chip封装,适配1.8-2.5V IO电压以及0.9-1V core电压。

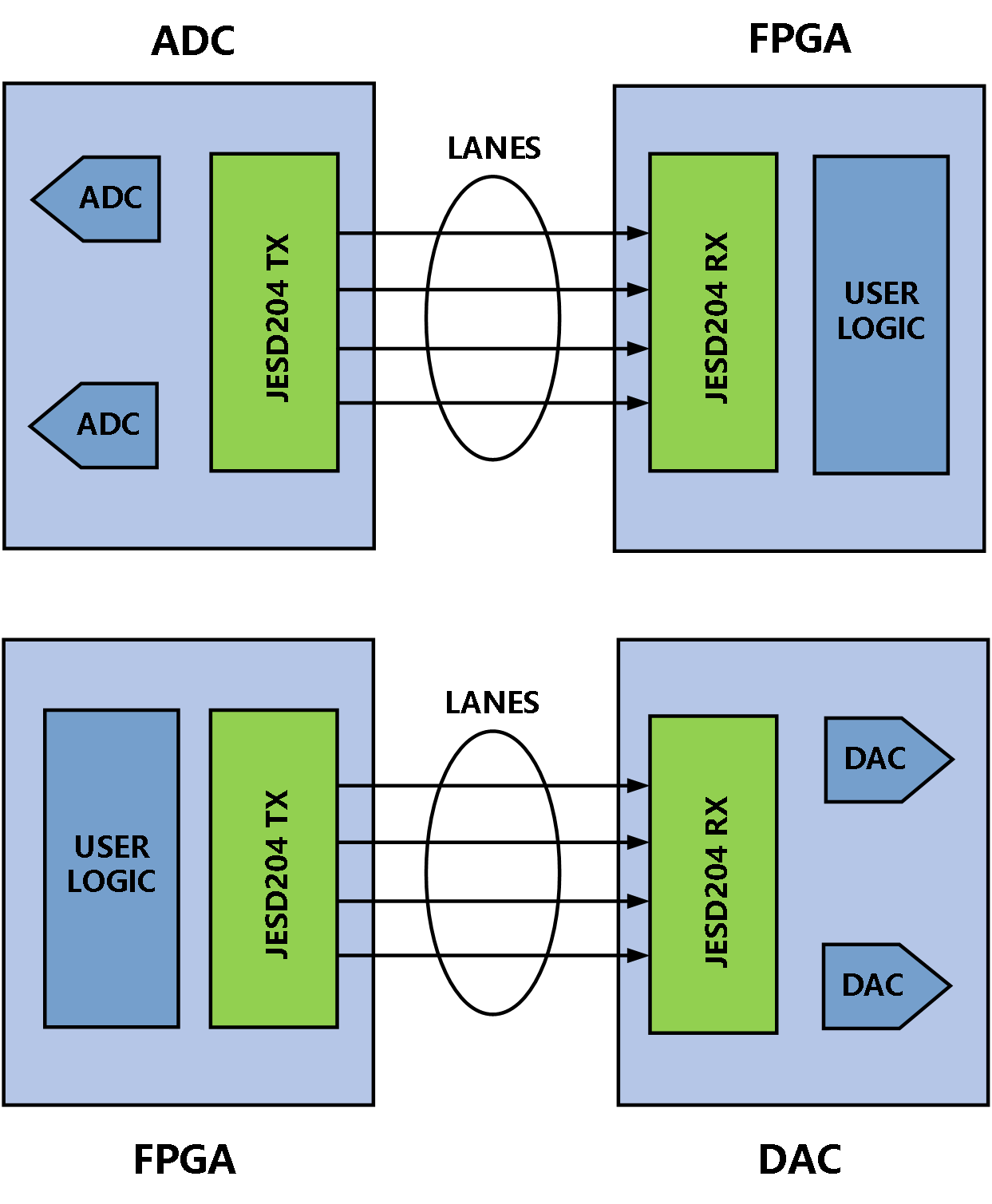

图2:204B PHY TX端8GHz时钟眼图质量

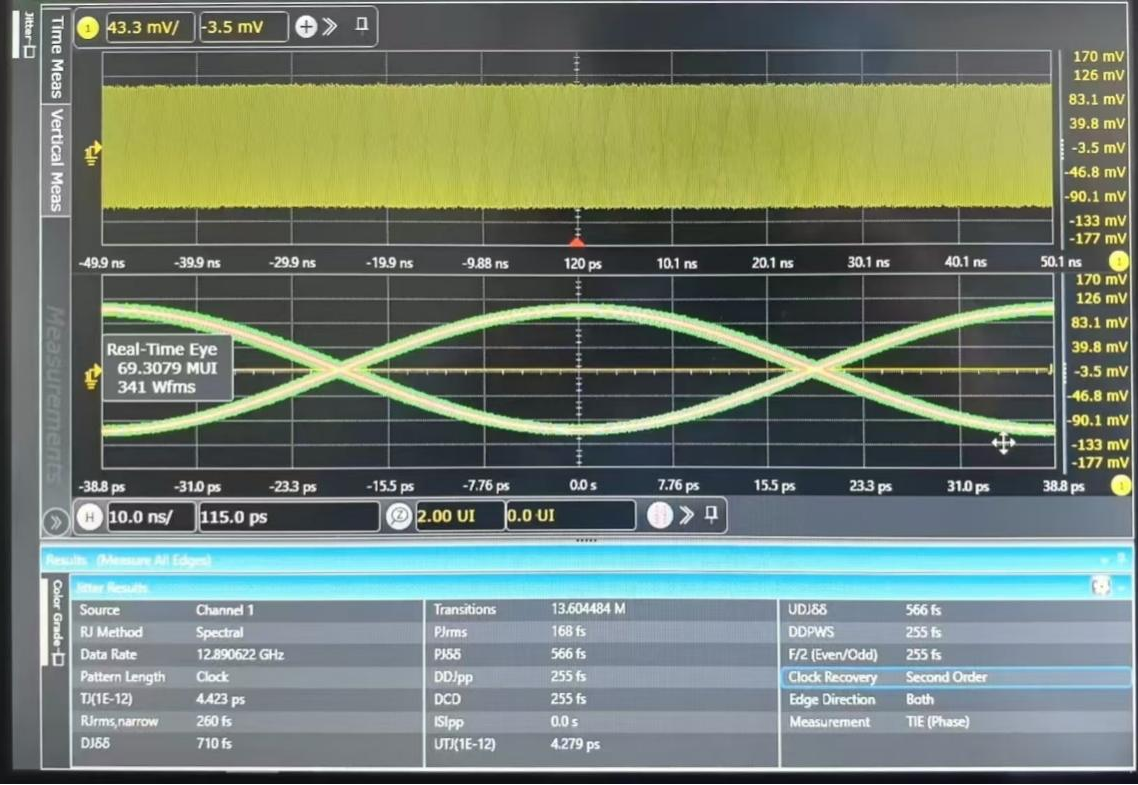

图3:204B PHY TX端16Gbps眼图质量

图4:204C PHY TX端12.89GHz眼图质量

图5:204C PHY TX端25.78125Gbps眼图质量

经实测验证,牛芯半导体JESD204B/C IP在不同速率模式下均保持优异的信号质量,眼图清晰、抖动指标良好,为高速数据稳定传输提供可靠保障,已获得多家知名厂商的认可和采用。国内某公司目前已在其模数转换器产品中集成了牛芯6.4Gbps JESD204B协议高速串行接口,相关方案可实现对标芯片的替换应用。该产品已经成功批量应用于医疗影像领域设备。此外,牛芯半导体基于28nm工艺,自主研发的25Gbps JESD204C TX PHY及Controller已成功适配某公司的8bit 64GSPS、12bit 16GSPS、12bit 40GSPS等多款ADC芯片产品,其中8bit 64GSPS的ADC芯片已实现量产出货,为高端数据转换应用提供稳定支撑。目前,最新发布的JESD204D标准已将最大传输速率提升至112Gbps,标志着接口技术正朝着更高速度、更高效率和更高的可靠性不断演进。对于接口IP开发者而言,挑战不仅在于追赶速率指标,更在于如何在速率提升的同时,维持信号完整性、降低功耗、简化系统集成。未来,牛芯半导体将持续深耕JESD204 IP的设计与实现,为模数转换芯片的性能突破提供坚实支撑,助力行业迎接下一轮通信与计算浪潮。

目前,最新发布的JESD204D标准已将最大传输速率提升至112Gbps,标志着接口技术正朝着更高速度、更高效率和更高的可靠性不断演进。对于接口IP开发者而言,挑战不仅在于追赶速率指标,更在于如何在速率提升的同时,维持信号完整性、降低功耗、简化系统集成。未来,牛芯半导体将持续深耕JESD204 IP的设计与实现,为模数转换芯片的性能突破提供坚实支撑,助力行业迎接下一轮通信与计算浪潮。