Overview

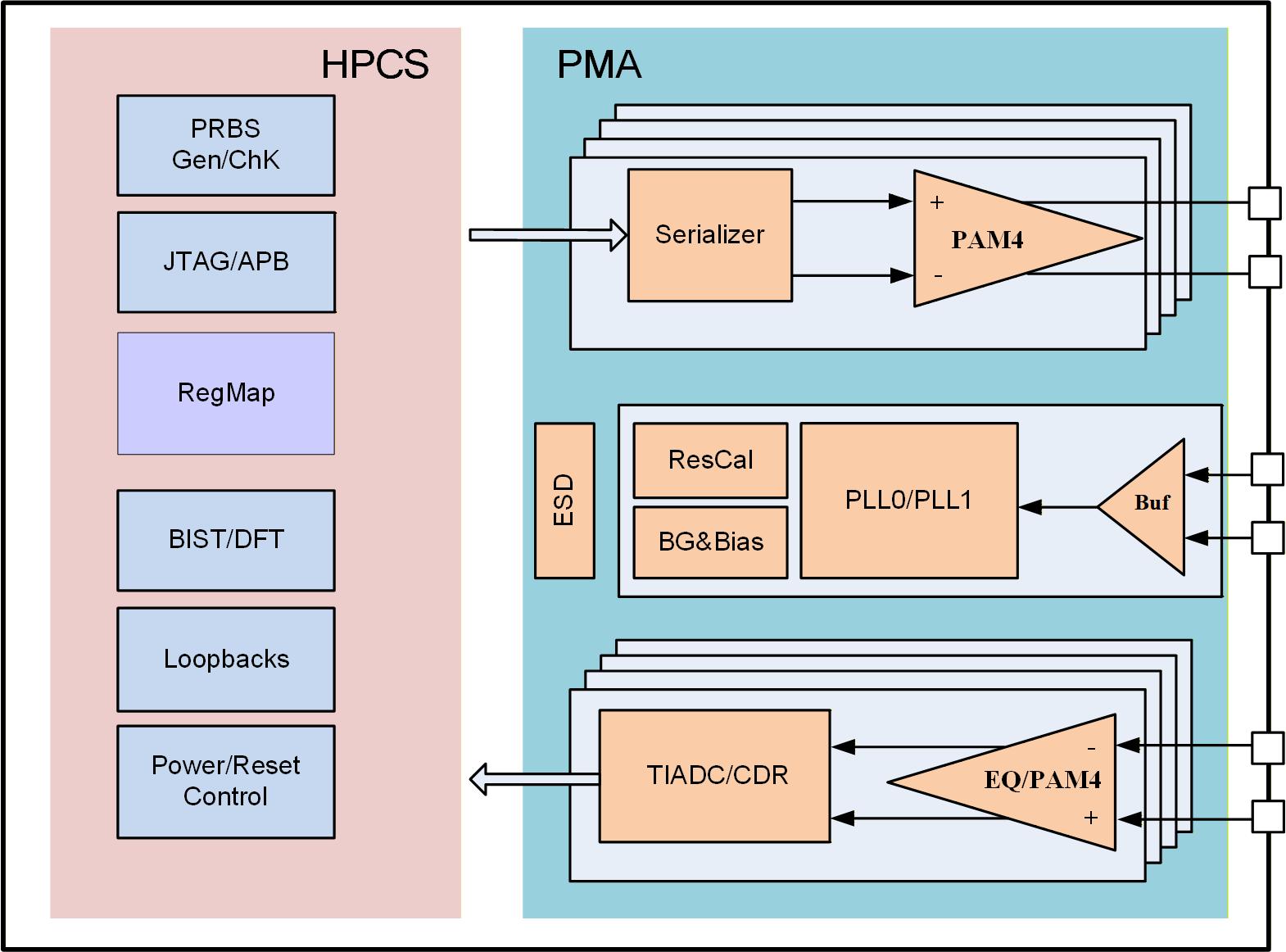

The KNiulink 64G SerDes IP core supports PAM4 signaling in the range of 32.0~64.0Gbps with scrambled data. Non-return-to-zero (NRZ) signaling is supported in the range of 1.25~ 32.0 Gbps. Either scrambled or block coded (for example, 8B/10B) data is supported for 1.25 ~12.5 Gbps in NRZ mode. However, scrambled data is required for data rates greater than 12.5 Gbps.

The 64G SerDes IP cores are intended for use as a chip-to-chip or a card-to-card connection mechanism.

Highlights

- • Support PCl Expression Gen6 & Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- • Support 64Gbps PCIe Gen6, 32 Gbps PCle Gen5, 16 Gbps PCle Gen4, 8 Gbps PCleGen3, 5 Gbps PCle Gen2 and 2.5 Gbps PCle Gen1 Test mode

PAM4 support 32~64Gbps;

NRZ support 2.5~32Gbps; - • Highly customizable PMA configuration (controlled by PCS), X4 per Quad;

- • Support Data Width:10bit, 16bit, 20bit, 32bit, 40bit, 64bit, 80bit, 128bit, 160bit

- • Support PCIe 6.0/5.0 aggregation and bifurcation up to x16 PHY configuration;

• Supports PCIe L1-substate power managements and Separate Refclk Independent SSC; - • Support SRIS/SRNS;

• Support Beacon signaling;

• TX support Back-channel Training; - • Adaptive and configurable RX continuous time linear equalizer(CTLE) and VGA;

- • Adaptive and programmable TX equalization;

- • Support Test Modes: Boundary Scan (ACJTAG), IDDQ, Scan, Diagnostics (serial and parallel loopback), and Normal Operation;

• Built-in self-test (BIST) features for production; - • Advanced, built-in diagnostics including on-chip eye monitor;

• PLL: one PLL per common, based on low jitter LC-tank oscillators; - • Configurable PCS with extensive debug options;

• A wide range of divided clock frequencies for external-to-PHY usage;

• A reference clock repeater for other modules; - • Support on chip resistance calibration mechanism;

• Support advanced process technology

• Flip-Chip package supported

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • Support PCl Expression Gen6 & Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- • Support 64Gbps PCIe Gen6, 32 Gbps PCle Gen5, 16 Gbps PCle Gen4, 8 Gbps PCleGen3, 5 Gbps PCle Gen2 and 2.5 Gbps PCle Gen1 Test mode

PAM4 support 32~64Gbps;

NRZ support 2.5~32Gbps; - • Highly customizable PMA configuration (controlled by PCS), X4 per Quad;

- • Support Data Width:10bit, 16bit, 20bit, 32bit, 40bit, 64bit, 80bit, 128bit, 160bit

- • Support PCIe 6.0/5.0 aggregation and bifurcation up to x16 PHY configuration;

• Supports PCIe L1-substate power managements and Separate Refclk Independent SSC; - • Support SRIS/SRNS;

• Support Beacon signaling;

• TX support Back-channel Training; - • Adaptive and configurable RX continuous time linear equalizer(CTLE) and VGA;

- • Adaptive and programmable TX equalization;

- • Support Test Modes: Boundary Scan (ACJTAG), IDDQ, Scan, Diagnostics (serial and parallel loopback), and Normal Operation;

• Built-in self-test (BIST) features for production; - • Advanced, built-in diagnostics including on-chip eye monitor;

• PLL: one PLL per common, based on low jitter LC-tank oscillators; - • Configurable PCS with extensive debug options;

• A wide range of divided clock frequencies for external-to-PHY usage;

• A reference clock repeater for other modules; - • Support on chip resistance calibration mechanism;

• Support advanced process technology

• Flip-Chip package supported

Applications

-

Data Center

-

High Performance Computing

-

Storage

-

Communications